As Unmanned Aerial Vehicles (UAVs) assume a greater role in the Department of Defense’s (DoD’s) plans for the future, program managers are placing more emphasis on improving the payload technology they use to conduct Intelligence, Surveillance, and Reconnaissance (ISR) missions. To solve this challenge, industry is paying greater attention to the processor complex powering these systems, which must evolve in compute density and performance to execute the complex processing tasks required by the next generation of UAVs.

“There’s a lot of interest in the ability to geo-locate and geo-register targets; elevated target recognitions; multi-modality fusion to increase the decision capacity so when you look at things like Synthetic Aperture Radar (SAR) systems combined with Electro-optical/Infrared (EO/IR) you get some benefit from fusing that capability to increase your decision capacity,” says David French, Director of Business Development, Military and Aerospace at GE Intelligent Platforms in San Diego, CA (defense.ge-ip.com). “All of that can be relatively compute-intensive, so that’s probably what is driving a lot of the payload designs today – evermore compute capacity.”

“There are several technologies that make processing more attractive in the UAV,” says Dennis Smith, Vice President of Engineering at Themis Computer in Fremont, CA (www.themis.com). “Primarily high core count, low-power CPUs, along with adjunct FPGAs or GPGPUs, allows for this to be realized close to the point of use. In the past, SIGINT has been a ground-based task because of the sheer volume, weight, and power needed to incorporate computing in the aircraft. The latest CPUs, with their high transistor count, have been able to deliver more processing cores, larger memory, and a host of general purpose I/O all in a single package.”

FPGAs are not the only solution to this problem, as GPGPU technology continues to improve and is much more cost-effective than FPGAs. “Using an FPGA approach provides the highest performance and lowest latency,” Smith continues. “However, there is a penalty in cost, flexibility, and power compared to a general purpose, software-driven approach. Some of the lost speed can be augmented through the use of large core count GPGPUs. If the application can tolerate increased latency and code complexity, using a GPGPU can provide a lot of value over a pure FPGA approach.”

“If you look at technology trends I think probably the most impactful has been the introduction of GPGPU processing,” agrees French. “It really does offer a significant increase in the performance of ISR-type processing – if it’s radar, EO/IR, or other payloads – and the fusing of that data in some cases. It’s probably going to continue with higher core counts and more density, as we’ve seen GPUs’ core count basically double every couple of years.”

VPX architectures

Advances in processor technology have enabled performance gains in ISR payloads, but capability improvements and complexity also require a standardized system-level architecture to reduce cost and complexity, Smith says. Through the use of Open Architectures (OAs) such as VPX, application engineers and integrators are afforded an adaptable system that also allows compute resources to move closer to the sensors themselves, he continues.

“Delivering all of this capability at low cost requires a standards-based packaging and interconnect approach such as has been defined in the VITA 74 standard,” says Smith.“By dividing the processing task into multiple pluggable modules, the SIGINT problem can be easily segmented and optimized for a given application. Each of the module slots can be used to do pre-processing on the data stream before getting to the main processor for storage. The result is application flexibility,” he continues.

“That’s why a lot of ISR systems are going to 6U VPX, because you have to pre-process those signals,” says Ray Alderman, Chairman of the Board for VITA, headquartered in Scottsdale, AZ (www.vita.com).

ISR payload design challenges

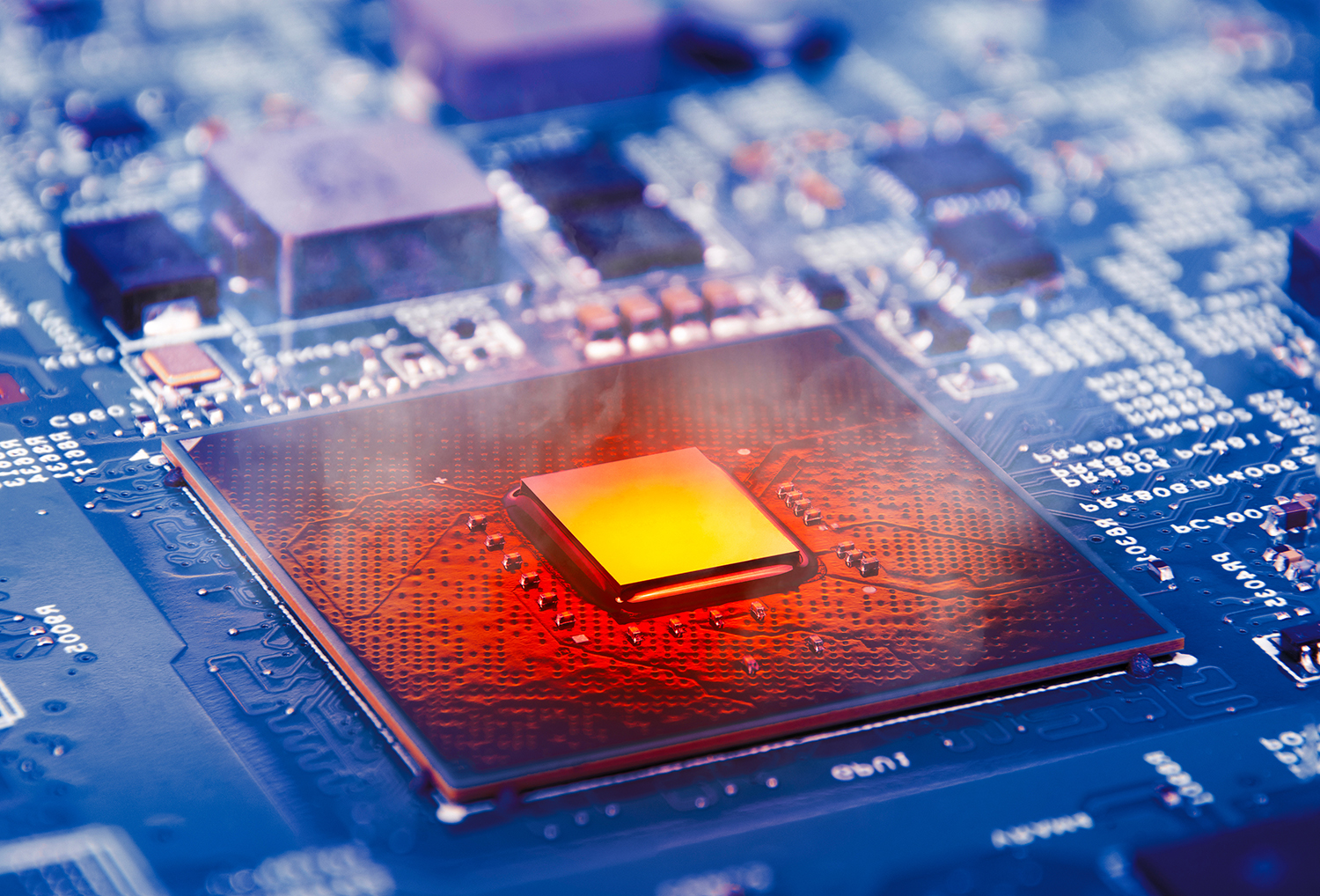

While advances in compute technology are enhancing ISR technology onboard UAV platforms, the unmanned vehicles face challenges in terms of Size, Weight, and Power (SWaP). Because of this, high-performance processing elements require hardware platforms that can support the additional size and heat that they generate, Alderman says.

“3U boards are [still] used a lot in UAVs, primarily for mission computers,” he continues. “It just doesn’t have the space to do the big GPGPUs and the memory arrays and all the I/O and high-speed interfaces. You can do some lower-end stuff on SIGINT and reconnaissance, and those guys are getting really good at packing their computing power on a 3U board. The more stuff you pack on a 3U board, your heat density goes up. There’s this nasty relationship between computing power and power consumption and heat density.”

Alderman says incorporating GPGPUs with their increased memory and horsepower is a must on larger UAVs that are switching to 6U VPX. “When you have a lot of processing and pre-processing to do, you have to go to 6U,” he adds.

“Because the latest high-performance signal processing devices, like FPGAs and GPUs, can consume significant power, two big challenges are managing cooling and developing adaptive techniques for power reduction,” says Rodger Hosking, Vice President of Pentek, Inc. in Upper Saddle River, NJ (www.pentek.com).

“Thermal efficiency is actually becoming one of the more critical items just because of the limited capacity to cool and the level of computational parts they require at the same time,” says GE’s French. “A lot of people don’t think about the packaging and the cooling of it, but that’s actually becoming a limiting factor in some cases – when we’re delivering platforms that have this compute capacity, and the system being weight-sensitive. Just a few extra pounds saved can mean several minutes longer for an ISR platform to stay on station, for instance, or extend the range of a platform, which is very important. Because these are UAVs, they’re very sensitive to weight. SWaP is a constant refrain; it’s never going to stop.”

Future ISR payload tech on UAVs

For the foreseeable future, most ISR payload upgrades will occur in UAVs already in existence. However, even with budget cuts industry insiders still see growth in smaller UAV platforms.

“Most of the growth will be in the small to medium size platforms, primarily because of cost, but also due to the resources required to operate and support the UAV platform. Small and medium size UAVs can find their way into a larger array of applications than the large platforms,” Smith says. Hosking also foresees increased autonomous capabilities for surveillance missions on the smaller UAVs, which therefore reduces direct human control and leads to cost reductions.

Due to the continued Department of Defense (DoD) budget cuts, French thinks most of the innovation will occur on platforms that are already in existence, with continued improvement to ISR payloads. Although there is interest in reducing weight of payloads for smaller UAVs, larger UAVs (Group 4 and 5) will most likely drive innovation in ISR payloads, French continues.

“Whenever something is proven on a larger payload, there’s an immediate interest in reducing its size and capabilities. Affordability is going to be a limiting factor, and I think that’s going to drive things like open architecture and commonality across platforms,” French adds.